Last time, we introduced the basic concept of SDC. In the next few issues, we will walk through some of the most commonly used SDC commands. Although there are hundreds of SDC commands available, only a dozen or so are typically used in practice. Today, we’ll focus on clock-related commands, which play a crucial role in timing analysis.

There are several key commands related to clocks:

- Create_clock

- Create_generated_clock

- Set_clock_uncertainty

- Set_clock_groups

Before any timing constraints can be applied, it's essential to define the clock. In a synchronous circuit, the delay between two sequential elements must be less than one clock period. Once the clock is defined, the timing constraints for paths between these elements are automatically inferred. The clock specification typically includes three main elements: waveform, uncertainty, and clock group. These are often referred to as the "three pillars" of clock definition. When creating any clock, always verify that all three are properly set up.

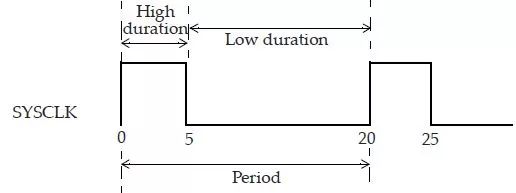

The Create_clock command is used to define the source, period, duty cycle, and edge timing of a clock signal. For example:

This clock can be described in an SDC script as follows:

create_clock -name SYSCLK -period 20 \

-waveform {0 5} [get_ports SCLK]

The waveform parameter defines the rising and falling edges. If no period is specified, the default is {0, period/2}.

Next, we have the Create_generated_clock command, which is used to define clocks derived from a master clock. This is especially useful when dealing with divided or multiplied clocks. For instance:

# Define master clock

create_clock -name CLKP -period 10 \

-waveform {0 5} [get_pins UPLL0/CLKOUT]

# Define generated clock at point Q

create_generated_clock -name CLKPDIV2 \

-source UPLL0/CLKOUT \

-master_clock CLKP -divide_by 2 [get_pins UFF0/Q]

Generated clocks are not treated as separate clock domains, so their timing paths still originate from the master clock. This helps avoid unnecessary recalculations during clock tree synthesis (CTS).

Another important concept is the Virtual Clock. Unlike real clocks, virtual clocks are not tied to any physical pin or port. They are often used to model off-chip timing requirements, such as input/output delays. For example:

# Define a virtual clock

create_clock -name VCLK -period 10 -waveform {0 5}

Virtual clocks are particularly useful when applying input/output timing constraints because they represent external clock sources more accurately.

The Set_clock_uncertainty command is used to account for variations in clock arrival times. It helps reduce the impact of jitter on the effective clock period. During setup checks, uncertainty reduces the available clock window, while during hold checks, it adds an extra margin.

For example:

set_clock_uncertainty -from VIRTUAL_SYS_CLK \

-to SYS_CLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK \

-to SYS_CLK -setup 0.3

set_clock_uncertainty -from SYS_CLK \

-to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK \

-to CFG_CLK -setup 0.1

Finally, the Set_clock_groups command is used to define relationships between different clock domains. This is critical for cross-domain timing checks. There are three common options:

- asynchronous – for unrelated clock domains

- physically_exclusive – for clocks that cannot be active at the same time on the same source

- logically_exclusive – for clocks that are mutually exclusive due to logic (e.g., via a MUX)

An example of using this command:

set_clock_groups -physically_exclusive \

-group {CLK1 CLK2} -group {CLK3 CLK4}

Properly defining clock groups is crucial to ensure accurate static timing analysis (STA). Always confirm these settings with your front-end team.

Clock definitions are fundamental to SDC, but there’s much more to explore. Each command has multiple options and use cases, and it's best to refer to the official documentation for in-depth understanding. As you continue working with SDC, you'll find that mastering these commands is essential for achieving accurate timing closure.

Outdoor Drop Cable,Ftth Cables,Fiber Optic Drop Cable,Drop Cable Fiber

Guangzhou Jiqian Fiber Optic Cable Co.,ltd , https://www.jqopticcable.com