Eliminating the risks associated with complex network SoC development is no longer a distant dream—it's now achievable for all design teams. In recent months, I've been exploring the advantages of using hardware-accelerated simulation to verify network system-on-a-chip (SoC) designs before chip fabrication. This article will focus on a new approach that bridges the gap between front-end and back-end verification in the same network design.

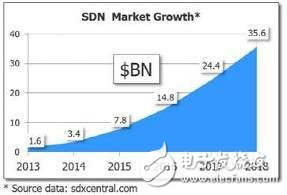

Before diving into the details, let’s take a closer look at this highly competitive market. As emerging markets like cloud computing, big data centers, and mobile applications continue to expand, software-defined networking (SDN) has become a key enabler. Figure 1 shows the rapid growth of the SDN market, which is projected to grow by 135% over the next two years.

Figure 1. SDN adoption is rising due to new markets such as cloud computing, big data centers, and mobile applications (Source: Lauro RizzatTI).

The rise of SDN has significantly increased design complexity, expanded the scale of designs, and added more ports. Figure 2 illustrates the growth in design complexity across key market segments.

Figure 2. Design complexity and gate count have grown with new SDN applications (Source: Lauro RizzatTI).

Design teams working on these large-scale SoCs are facing significant challenges. From most to least critical, these include:

1. Testing all port configurations.

2. Measuring and meeting performance and bandwidth expectations.

3. Ensuring the design supports all Ethernet OSI layer protocols.

4. Debugging hardware issues found during simulation and lab testing.

5. Verifying that the design can be reconfigured and executed as expected by software.

6. Achieving fast turnaround times for compilation, download, and execution.

7. Reducing the cost and time required to deploy the verification environment.

8. Evaluating and minimizing power consumption.

9. Reducing the chip package size.

Traditional software simulation or formal verification tools have not been sufficient to address these challenges. While they remain essential tools in the validation process, their use is typically limited to IP and subsystem-level verification, which is crucial in the early stages of complex SoC development—especially for network chips.

In today’s billion-dollar competition, only a hardware-driven verification engine can handle these challenges effectively, while keeping schedules tight to avoid revenue loss from delayed chip launches in the fast-growing network market.

As mentioned in my previous article, hardware-accelerated simulation has emerged as the top choice for front-end verification. Modern hardware accelerators offer near-infinite capacity to simulate even the largest designs, providing full visibility without instrumentation or compilation. They support high throughput, fast and predictable compile and recall times, and can serve multiple users efficiently. These systems can be deployed in various modes, including internal circuit emulation (ICE), virtual testing, low-power verification, power estimation, performance feature extraction, and testability design (DFT).

However, when verifying network SoCs with many ports—like 64 or more—the value of ICE has dropped significantly compared to a decade ago. The ICE setup requires external hardware like speed adapters to interface with real-world traffic at hundreds of megahertz, while the hardware-accelerated emulation runs at much lower speeds, such as one or several megahertz. This increases setup complexity, power consumption, and reduces reliability. It also makes reconfiguration slow and cumbersome, limiting access to a single local user and eliminating remote access. Worse, it creates uncertainty in debugging reproducibility, making it difficult to implement effective debug plans.

To overcome these limitations, many design teams are moving away from traditional ICE setups and adopting virtual test environments. These eliminate all hardware dependencies, including noise, power, cabling, and reliability, along with related costs. Virtual hardware can be created using a combination of software and synthesizable models, allowing easy reconfiguration before actual hardware is available. These environments run at hardware-accelerated simulation speeds, support multiple users and projects, and can be accessed remotely, even in a data center.

Guy Hutchison, a DAC 2016 expert group member and assistant vice president at Cavium, said: “For our design, we rely entirely on virtual technology. Partly because of the nature of our design—we don’t have a truly representative target that can handle 100 Gbps of traffic. The internal circuit simulator approach isn’t useful for us, so we use a completely virtual approach for all simulations.â€

Despite the benefits, creating a virtual test environment is no small task. In response, Mentor Graphics has developed VirtuaLAB, a comprehensive virtual environment designed to support front-end verification of application-specific SoCs. For network designs, VirtuaLAB includes an Ethernet Packet Generator and Monitor (EPGM) that generates, transmits, and monitors Ethernet packets for the design under test (DUT). It supports configurations such as 25GMII, 50GMII, 200GMII, and 400GMII, making it a powerful tool for modern SoC verification.

Huawei Glass,glass huawei,gorilla glass huawei,huawei phone glass

Dongguan Jili Electronic Technology Co., Ltd. , https://www.jlglassoca.com